#### **IT700 MAIN FEATURES**

- Low-cost powerline communication (PLC) modem and application solution in a single chip

- Incorporates Yitran's high performance Data Link Layer (DLL), Network Protocol (Y-Net) and extremely robust Physical Layer (PHY)

- Extended 8051 microcontroller with 256KB Flash for protocol stack and application

- **Protocol Controller Architecture** version: pre-programmed with communication stack

- **Open Solution Architecture** version: allows user to program application code together with the communication stack.

- Full home coverage even under adverse line conditions

- HomePlug<sup>®</sup> Command and Control ready

- Fully backward compatible with IT800 Series

#### APPLICATIONS

- Smart Grid Applications:

- Automated Meter Reading (AMR)

- Advanced Meter Management (AMM)

- Energy Management:

- Smart Home & Building Automation

- Home Appliance Control & Diagnostics

- Security and Access Control

- Environmental Control

- Commercial Applications:

- Street Light Control

- Vending Machine Control

- Signage Control

June 2008

A

#### Copyright © 2008, YITRAN Technologies Ltd. www.yitran.com

001\_IT700

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of YITRAN Technologies' products and disclaimers thereto appears at the end of this document. Other trademarks are property of their respective owners

## **1.** Communication Layer Features

### LAYER 1 (PHY)

- Patented DCSK modulation

- High immunity to signal fading, noise, impedance modulation and phase/ frequency distortions

- High in-phase and crossphase reliability

- Forward short-block soft decoding error correction mechanism and CRC-16

- Complies with FCC, ARIB and EN50065-1-CENELEC regulations

- FCC and ARIB bands bit rate:

- 7.5Kbps Standard Mode (SM)

- 5.0Kbps Robust Mode (RM)

- 1.25Kbps Extremely Robust

- Mode (ERM) • CENELEC band bit rate:

- 2.5Kbps Robust Mode (RM)

- 0.625Kbps Extremely Robust Mode (ERM)

### LAYER 2 (DLL)

- Up to 1023 logical networks and 2047 nodes per network

- Acknowledged and Unacknowledged data transmission services

- Re-transmission mechanism

- Automatic rate control

- Adaptive Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA) channel access

- Fragmentation and reassembly to support full Ethernet packet transmission

### LAYER 3 (NETWORK)

- Supports 1000 different, overlapping networks

- Supports 2000 nodes in each network

- Master-Slave and Peer-to-Peer Network Configurations

- Plug & Play Network Setup

- Automatic logical network creation

- Automatic node address allocation

- Automatic and adaptive Routing Service (Tree topology)

- Network Parameter Recovery

- Failure Detection

- Full security Suite including AES 128-bit encryption with 32 bit authentication

# 2. IT700 General Description

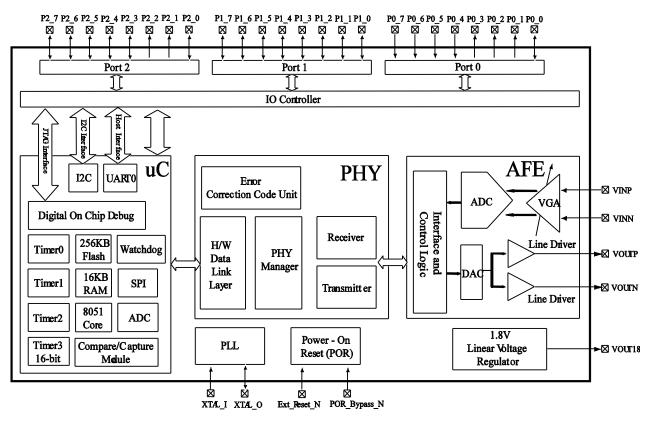

The IT700 is a highly integrated System-on-a-Chip (SoC) powerline communication (PLC) modem. It incorporates Yitran's extremely reliable Physical Layer (PHY), high performance Data Link Layer (DLL) and Yitran Network Layer (Y-Net) protocol.

An integrated microcontroller with extended 8051 core, 256KB Flash memory, 16KB RAM and 24 general purpose I/Os implements the protocol stack and offers the required flexibility to implement various protocols and applications. The microcontroller's UART interface provides the connection to an external Host and application controller. The I<sup>2</sup>C interface connects an optional external EEPROM for configuration parameter storage.

The IT700 modem core uses Yitran's patented Differential Code Shift Keying (DCSK) advanced spread spectrum modulation technique. DCSK enables extremely robust communication over existing electrical wiring with data rates up to 7.5Kbps. In addition to the inherent interference immunity provided by DCSK modulation, the device utilizes several mechanisms for enhanced communication robustness, such as a patented forward short-block soft-decoding error-correction algorithm and special synchronization algorithms.

The integrated Analog Frontend provides differential inputs and line driver outputs to connect via an external line filter and coupler to the power transmission lines. An integrated Phase Locked Loop Circuit allows the operation of the IT700 with a choice of different crystal oscillators. An integrated Power On Reset (POR) circuitry eliminates the need for any external reset components and provides an autonomous, safe power-up and power-down reset to the chip. The integrated 1.8V voltage regulator allows the IT700 to operate from a single 3.3V supply voltage.

The IT700 complies with worldwide regulations (FCC part 15, ARIB and CENELEC bands) and is an ideal solution for a variety of "No New Wires" narrowband PLC applications.

The IT700 will be available in two versions:

The **Protocol Controller Architecture** version has Yitran's Y-Net network layer protocol (layer 3) pre-programmed into the 8051 microcontroller's Flash memory. A UART interface and simple command language provide seamless connection to an external Host controller and simplify application development. In this version you have no access to the microcontroller's unused memory space, peripheral functions and general purpose I/Os.

The **Open Solution Architecture** version allows you to utilize the IT700 microcontroller's peripheral functions, such as timers, interrupts, communication interfaces, A/D, spare memory resources and general-purpose I/Os to implement your own application code, thereby eliminating the requirement for an external host controller. An Application Programming Interface (API) enables the easy integration of your application code with Yitran's Network Layer code.

This advanced information document covers the Protocol Controller Architecture version only; release of the Open Solution Architecture version is scheduled for a future date.

# **3. Pinout and Pin Description**

## 3.1 Pinout

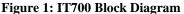

The following figure shows the IT700 QFN56 lead-free package pinout:

## **3.2** Pin Description

The functionality of the IT700 pins is described in Table 2. The pin type format used is xx/yy and the options for the xx and yy fields are shown in the following table:

#### Table 1: Pin Type Syntax

| XX | Description     | уу | Description        |

|----|-----------------|----|--------------------|

| Ι  | Input           | PD | Internal Pull-Down |

| 0  | Output          | PU | Internal Pull-UP   |

| IO | Input or Output | А  | Analog             |

| Pin #   | Pin Name  | Туре  | Description                                                |  |

|---------|-----------|-------|------------------------------------------------------------|--|

| 1 111 # | Alternate | Type  | Description                                                |  |

|         | Functions |       |                                                            |  |

| 1       | P1_6      |       | General-purpose input/output                               |  |

| 1       | INT1      | IO/PU | External Interrupt input                                   |  |

| 2       | P1_5      |       | General-purpose input/output                               |  |

| 2       | INT0      | IO/PU | External Interrupt input                                   |  |

| 3       | P1_4      |       | General-purpose input/output                               |  |

| 5       | CAPTURE0  | IO/PU | Timer T2 Capture/Compare input 0                           |  |

|         | INT3      | 10/10 | External Interrupt input                                   |  |

| 4       | P1_3      |       | General-purpose input/output                               |  |

| 4       | INT2      | IO/PU | External Interrupt input                                   |  |

| 5       | P1_2      |       | General-purpose input/output                               |  |

| 5       | T2EX      | IO/PU | Timer T2 External event reload input                       |  |

|         | INT6      | 10/10 | External Interrupt input                                   |  |

| 6       | VDD18     | Power | +1.8V supply voltage: must be connected to VOUT18 (pin 28) |  |

| 7       | VSS18     | Power | Digital Ground                                             |  |

| 8       | P1_1      | 10001 | General-purpose input/output                               |  |

| Ũ       | T2        | IO/PU | Timer T2 external clock or gated clock input               |  |

|         | INT5      |       | External Interrupt input                                   |  |

| 9       | P1 0      |       | General-purpose input/output                               |  |

|         | TJEX      | IO/PU | Timer T3 External event reload input                       |  |

| 10      | P2 7      |       | General-purpose input/output                               |  |

|         | SDA       | IO/PU | I <sup>2</sup> C Serial Data (SDA)                         |  |

| 11      | P2_6      | IO/PU | General-purpose input/output                               |  |

|         | SCL       | 10/PU | I <sup>2</sup> C Serial Clock Line (SCL)                   |  |

| 12      | P2_5      | IO/PU | General-purpose input/output                               |  |

|         | SCK       | 10/PU | SPI Master Clock Output (SCK)                              |  |

| 13      | VDD33     | Power | +3.3V supply voltage                                       |  |

| 14      | VSS33     | Power | Digital Ground                                             |  |

#### Table 2: IT700 Pin Description

| Pin # | Pin Name           | Туре  | Description                                                                                    |  |

|-------|--------------------|-------|------------------------------------------------------------------------------------------------|--|

|       | Alternate          | ~ 1   | L L                                                                                            |  |

|       | Functions          |       |                                                                                                |  |

| 15    | P2_4               | IO/PU | General-purpose input/output                                                                   |  |

| 15    | <sup>13</sup> MOSI |       | SPI Master Data Output (MOSI)                                                                  |  |

| 16    | P2_3               | IO/PU | General-purpose input/output                                                                   |  |

| 10    | MISO               | 10/10 | SPI Master Data Input (MISO)                                                                   |  |

|       | P2_2               |       | General-purpose output                                                                         |  |

| 17    | RX_LED             | O/PU  | Receive LED                                                                                    |  |

|       | FMODE_1            |       | Functional Mode select, Bit 1 (sampled during Reset)                                           |  |

| 10    | P2_1               | O/PU  | General-purpose output                                                                         |  |

| 18    | TX_LED             |       | Transmit LED                                                                                   |  |

|       | FMODE_0            |       | Functional Mode select, Bit 0 (sampled during Reset)                                           |  |

| 19    | P2_0<br>CAPTURE1   | IO/PU | General-purpose input/output                                                                   |  |

| 20    | VDD18              | Power | Timer T2 Capture/Compare input 1<br>+1.8V supply voltage, must be connected to VOUT18 (pin 28) |  |

| 20    | VDD18<br>VSS18     | Power | Digital Ground                                                                                 |  |

| 21    | ADC_IN             | I/A   | Analog to Digital Converter Input                                                              |  |

| 22    | N/C                | I     | Not Connected                                                                                  |  |

| 23    | VINP               | I/A   | Positive Differential Input from powerline coupler/filter                                      |  |

| 25    | VINN               | I/A   | Negative Differential Input from powerline coupler/filter                                      |  |

| 26    | VSSRX              | Power | Analog Ground                                                                                  |  |

| 27    | VDDRX              | Power | +3.3V Analog Power Supply                                                                      |  |

| 28    | VOUT18             | Power | +1.8V Voltage Regulator Output                                                                 |  |

| 29    | ISENSEP            | I/A   | Current Sense Input                                                                            |  |

| 30    | VDDTX              | Power | +3.3V Analog Power Supply                                                                      |  |

| 31    | VOUTN              | O/A   | Negative Differential Line Driver Output to powerline coupler                                  |  |

| 32    | VSSTX              | Power | Analog Ground                                                                                  |  |

| 33    | VSSTX              | Power | Analog Ground                                                                                  |  |

| 34    | VOUTP              | O/A   | Positive Differential Line Driver Output to powerline coupler                                  |  |

| 35    | VDDTX              | Power | +3.3V Analog Power Supply                                                                      |  |

| 36    | VDD33F             | Power | +3.3V Digital Power Supply                                                                     |  |

| 37    | VSSF               | Power | Digital Ground                                                                                 |  |

| 38    | VDD18F             | Power | +1.8V supply voltage: must be connected to VOUT18 (pin 28)                                     |  |

| 39    | XTAL_I             | Ι     | External Oscillator Input                                                                      |  |

| 40    | XTAL_O             | IO    | External Oscillator Output                                                                     |  |

| 41    | VDD18A             | Power | +1.8V analog supply voltage: must be connected to VOUT18<br>(pin 28)                           |  |

| 42    | VSS18A             | Power | Analog Ground                                                                                  |  |

| 43    | N/C                | I/PU  | Not Connected                                                                                  |  |

| 44    | POR_BYPASS_N       | I/PU  | Power On Reset (POR) Bypass, active low                                                        |  |

| 45    | EXT_RESET_N        | I/PU  | External reset, active low. Only required if POR is disabled                                   |  |

|       | P0_7               |       | General-purpose input                                                                          |  |

| 46    | TMS                | I/PU  | Microcontroller JTAG Debug interface TMS signal                                                |  |

|       | TMS_FLASH          |       | Flash JTAG programming interface TMS signal                                                    |  |

| Pin # | Pin Name<br>Alternate | Туре    | Description                                                                                    |

|-------|-----------------------|---------|------------------------------------------------------------------------------------------------|

|       | Functions             |         |                                                                                                |

| 17    | P0_6                  | I (DI I | General-purpose input                                                                          |

| 47    | TDI<br>TDI FLASH      | I/PU    | Microcontroller JTAG Debug interface TDI signal<br>Flash JTAG programming interface TDI signal |

|       | P0_5                  |         | General-purpose input                                                                          |

| 48    | TCK                   | I/PU    | Microcontroller JTAG Debug interface TCK signal                                                |

|       | TCK_FLASH             |         | Flash JTAG programming interface TCK signal                                                    |

| 49    | P0_4                  | I/PU    | General-purpose input                                                                          |

| 49    | RXD                   | I/I U   | UART Receive Data In (RXD)                                                                     |

|       | P0_3                  |         | General-purpose output                                                                         |

| 50    | TXD                   | O/PU    | UART Transmit Data Out (TXD)                                                                   |

|       | PLL_FMODE_1           |         | PLL Mode select, Bit 1 (sampled during Reset)                                                  |

|       | P0_2                  |         | General-purpose output                                                                         |

| 51    | PLL_FMODE_0           | O/PU    | PLL Mode select, Bit 0 (sampled during Reset)                                                  |

| 51    | TDO                   | 0/10    | Microcontroller JTAG Debug interface TDO signal                                                |

|       | TDO_FLASH             |         | Flash JTAG programming interface TDO signal                                                    |

|       | P0_1                  |         | General-purpose output                                                                         |

| 52    | FMODE_2               | O/PU    | Functional Mode select, Bit 2 (sampled during Reset)                                           |

| 0-    | RTCK                  | 0/1 0   | Microcontroller JTAG Debug interface RTCK signal                                               |

|       | TOEN_FLASH            |         | Flash JTAG programming interface TOEN signal                                                   |

|       | P0_0                  | 10 777  | General-purpose input/output                                                                   |

| 53    | T3                    | IO/PU   | Timer T3 external clock or gated clock input                                                   |

|       | TRST_FLASH            |         | Flash JTAG programming interface TRST signal                                                   |

|       | P1_7                  |         | General-purpose input/output                                                                   |

| 54    | AdcExtTrig            | IO/PU   | ADC External Trigger input                                                                     |

|       | INT4                  | D       | External Interrupt input                                                                       |

| 55    | VDD33                 | Power   | +3.3V Supply voltage                                                                           |

| 56    | VSS33                 | Power   | Digital Ground                                                                                 |

# 4. Electrical Characteristics

## 4.1 Absolute Maximum Operating Conditions

These are stress ratings only: functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Stresses beyond those listed under "Absolute Maximum Operating Conditions" may cause permanent damage to the device. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

| Power supply voltage, VDD33 (max) | 3.6V                                     |

|-----------------------------------|------------------------------------------|

| Power supply voltage, VDD33 (min) | 0.3V                                     |

| Input voltage, VI (max)           | VDD+0.3V, max. 3.6V                      |

| Input voltage, VI (min)           |                                          |

| Storage temperature range         | $-40^{\circ}C \text{ to } +125^{\circ}C$ |

## 4.2 Recommended Operating Conditions

| Rating                                   | Symbol               | Minimum               | Nominal         | Maximum          | Unit  |

|------------------------------------------|----------------------|-----------------------|-----------------|------------------|-------|

| Power Supply Voltage                     | VDD33                | 3.0                   | 3.3             | 3.6              | V     |

| Power Supply Voltage                     | VDD18                | Connect to chip       | 's 1.8V voltage | regulator output | V     |

|                                          |                      |                       | VOUT18          |                  |       |

| Total Maximum Supply                     | IDD <sub>33max</sub> | no load on            |                 | 500              | mA DC |

| Current                                  |                      | digital outputs       |                 |                  |       |

| Average Power Consumption                | IDD <sub>33avg</sub> | During                | 75              |                  | mA DC |

|                                          | )                    | Reception             |                 |                  |       |

| High Level Input Voltage                 | V <sub>IH</sub>      | 2                     |                 | VDD+0.3 / 3.6    | V     |

| Low Level Input Voltage                  | V <sub>IL</sub>      | 0                     |                 | 0.8              | V     |

| High Level Output Voltage <sup>(1)</sup> | V <sub>OH</sub>      | at I <sub>DOmax</sub> |                 | 3.5              | V     |

| Low Level Output Voltage <sup>(1)</sup>  | V <sub>OL</sub>      | at I <sub>DOmax</sub> |                 | 0.4              | V     |

| Source and Sink Current <sup>(2)</sup>   | I <sub>DO</sub>      | Max. 5 I/Os at        |                 | 8                | mA    |

|                                          |                      | same time             |                 |                  |       |

| Internal Operating Frequency             | Fosc                 |                       | 46.08           |                  | MHz   |

| Crystal Overall Accuracy                 |                      |                       | 120             |                  | PPM   |

| Operating Temperature Range              | $T_0$                | -40                   | 25              | +85              | °C    |

Note: <sup>(1)</sup> At maximum sink/source current <sup>(2)</sup> Digital I/O pins, max. 5 outputs sink/source at the same time

# 5. Chip Configuration

## 5.1 Phase Locked Loop (PLL)

The IT700 has an integrated Phase Locked Loop (PLL) circuit that allows operating the device with different input clock frequencies.

The PLL operating mode is determined by sampling pins PLL\_FMODE\_1 (P0\_3) and PLL\_FMODE\_0 (P0\_2) during Reset. Table 3 shows the different PLL configurations and the required crystal input clock frequency for each mode.

| PLL_FMODE_1<br>(P0_3) | PLL_FMODE_0<br>(P0_2) | PLL state  | Crystal<br>Frequency<br>[MHz] | PLL OUT<br>[MHz] |

|-----------------------|-----------------------|------------|-------------------------------|------------------|

| 1                     | 1                     | active     | 5.12                          | 46.08            |

| 0                     | 1                     | active     | 15.36                         | 46.08            |

| 1                     | 0                     | active     | 15.36                         | 46.08            |

| 0                     | 0                     | Power down | 46.08                         | Bypassed         |

#### Table 3: PLL Mode Selection

### 5.2 IT700 Operating Modes

The IT700 chip operating mode is determined by sampling pins FMODE\_0 (P2\_1), FMODE\_1 (P2\_2) and FMODE\_2 (P0\_1) during Reset. Those pins are internally pulled high, which defaults to selecting the Protocol Controller Architecture mode. Do **not** pull these pins low during Reset.

| Table 4: IT700 Operating Mode Selection |         |         |     |  |

|-----------------------------------------|---------|---------|-----|--|

| 2                                       | FMODE_1 | FMODE_0 | Mod |  |

| FMODE_2 | FMODE_1 | FMODE_0 | Mode                                     |

|---------|---------|---------|------------------------------------------|

| (P0_2)  | (P2_2)  | (P2_1)  |                                          |

| 1       | 1       | 1       | Protocol Controller<br>Architecture Mode |

## 6. Host Interface

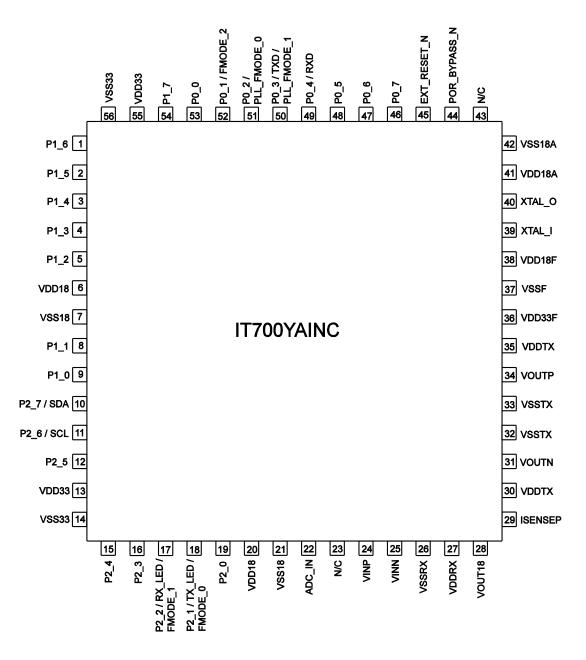

The IT700 Protocol Controller Architecture version comes with Yitran's Network layer pre-programmed into the integrated 8051 microcontroller's Flash memory. In this mode the device operates as a "closed" PLC modem chip. An external host and application controller is required to implement your application layer functionality. The host controller connects to the IT700 through a UART interface (RXD and TXD pins) with 38400 bps, 8 data bits, odd parity, 1 stop bit an no flow control.

Figure 3 shows the typical schematic connections for the IT700 Protocol Controller Architecture.

Figure 3: Typical Application Circuit, IT700 Protocol Controller Architecture

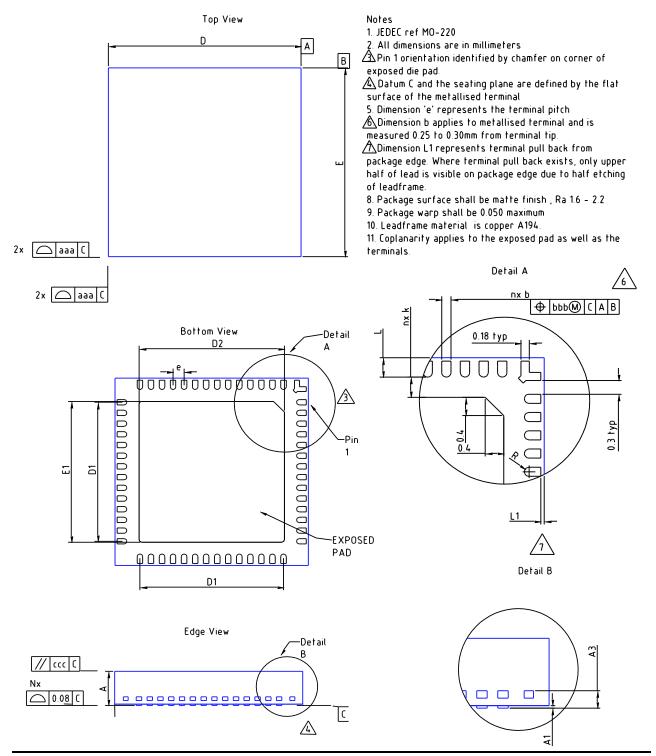

# 7. Mechanical Dimensions

### 7.1 Package Tolerances

|        | Common Dimensions (mm) |         |      |  |

|--------|------------------------|---------|------|--|

| Symbol | Min                    | Nom     | Max  |  |

| Α      | 0.85                   | 0.9     | 1    |  |

| A1     | 0                      | 0.02    | 0.05 |  |

| A3     |                        | .20 ref |      |  |

| D      | 6.9                    | 7       | 7.1  |  |

| D1     |                        | 5.2     |      |  |

| D2     | 5.2                    | 5.3     | 5.4  |  |

| Е      | 6.9                    | 7       | 7.1  |  |

| E1     |                        | 5.2     |      |  |

| E2     | 5.2                    | 5.3     | 5.4  |  |

| L      | 0.3                    | 0.4     | 0.5  |  |

| L1     |                        |         | 0.1  |  |

| b      | 0.15                   | 0.2     | 0.25 |  |

| Ν      |                        | 56      |      |  |

| e      |                        | 0.4     |      |  |

| k      | 0.2                    |         |      |  |

| R      | b min/2                |         |      |  |

| Т      |                        | 0.15    |      |  |

| Tolerances for Form & Position (mm) |       |    |  |

|-------------------------------------|-------|----|--|

| Symbol                              | Value |    |  |

| aaa                                 | 0     | .1 |  |

| bbb                                 | 0.0   | )7 |  |

| ссс                                 | 0     | .1 |  |

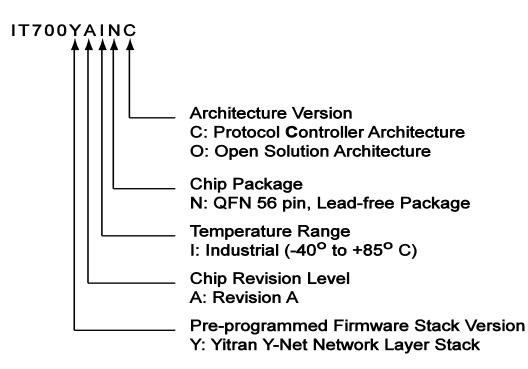

# 8. Ordering Information

The IT700 part naming convention for ordering parts is shown below:

### **Document Control**

| Rev | Date           | Description                                                                                                                          |

|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 |                |                                                                                                                                      |

| 1.1 |                |                                                                                                                                      |

| 1.2 |                |                                                                                                                                      |

| 1.3 | 1 March 2009   | Operating Conditions section updated<br>IT700 Protocol Controller Architecture figure updated<br>IT700 Pin Description table updated |

| 1.4 | September 2014 | Document format change                                                                                                               |

| 1.5 | November 2016  | Notice update                                                                                                                        |

### **Important Notice**

All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. Yitran Technologies Ltd. ("Yitran") reserves the right to make changes to its products, except for encryption and authentication algorithms, or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete.

Yitran warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with Yitran's standard warranty. Testing and other quality control techniques are utilized to the extent Yitran deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications"). Yitran's PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE–SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF Yitran's PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, the customer, to minimize inherent or procedural hazards, must provide adequate design and operating safeguards.

Yitran assumes no liability for applications assistance or customer product design. Yitran does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of Yitran covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. Yitran's publication of information regarding any third party's products or services does not constitute Yitran's approval, warranty or endorsement thereof.

**Yitran Tecnologies Ltd.** 6 HaGoren St. Omer 8496500 ISRAEL

T +972 8 958 0282 F +972 8 958 0281 yitran@yitran.com